Introduction

BJTs are often used in analog circuits where current amplification is needed. The equation which models the current gain of a transistor is given by: \begin{equation} \label{eq:1} \beta I_B = I_C \Longleftrightarrow \frac{I_C}{I_B}=\beta \end{equation} In the equation above, the current gain of the transistor (β) is defined by the ratio between the BJT collector and base currents. Unfortuinately, not all transistors have the same β due to deviations in manufacturing. The deviations in β need to be considered when constructing circuits such as a differential amplifier. If the amplification factors are too dissimilar, a circuit will not behave as expected. In order to measure these parameters, a family of curves for each BJT needs to be obtained. To obtain a family of curves for a BJT, one must perform a Collector-Emitter voltage DC sweep at targeted base-current operating points. A curve tracer streamlines this process by sequentially constraining a different $I_B$ before performing a DC sweep for each setting.A 4-bit Binary Counter (74HC193)

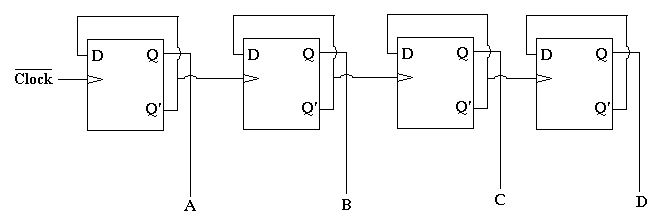

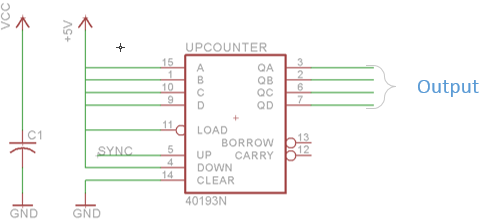

The binary counter is the first stage of this circuit. This stage utilizes a 74HC193 integrated circuit and can be realized by sequentially cascading four D-latches:.

N-Bit Digital-to-Analog Converter (DAC)

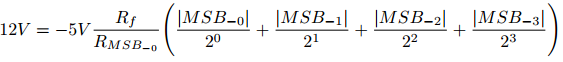

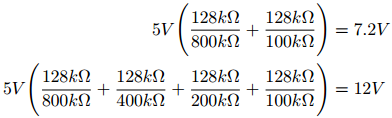

The second stage of the circuit will convert the binary counter's output registers to an analog waveform by adding them while accounting for the significance of each bit. An operational amplifier in a summing configuration is used to achieve this task:

Transconductance Inversion Amplifier

By this stage there we have a decreasing sawtooth wave. This step will invert the waveform to get the desired increasing sawtooth waveform. An inverting amplifier with is used as a buffer in this step:

Device Under Test (DUT)

After the waveform has been inverted, it is then fed into the DUT. In this case, the DUT is a BJT. By this point each binary number is summed, the waveform is stepped up by an increment and then inverted to get an increasing aliased sawtooth wave. The output from the subsequent steps provide the base current to the BJT so the family of curves can be produced when a collector-emitter DC sweep is executed.

Measurement

An oscilloscope and differential amplifier are used to obtain the family of curves using the XY plotting feature of the scope's display. The reason a differential amplifier is used is so the probe's impedance does not divide current from small voltage measurements.Up Counter

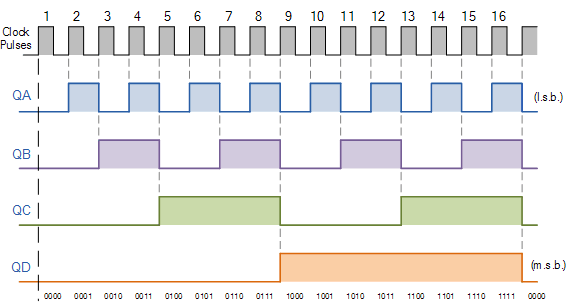

As discussed previously, the binary counter is connected to the sync pulse. In this application it is correct to call it an Up-Counter; in theconfiguration used the DOWN pin is pulled high while the UP pin is pulsed. When the up counter reaches its terminal value it rotates back to the base. The following timing chart shows the outputs of the 74HC193 as it counts from 0 to 10 in the up-coutner configuration:

4-Bit DAC

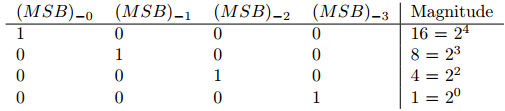

Since we are adding 4 bits from the counter, this stage of the design needs four inputs. These inputs create the linear terms necessary in the KCL equations. The input resistances (R1, R2, R3, R4) are calculated so the output of the amplifier accurately reflects the magnitude of the counter for each cycle. This table shows the magnitude weighting of each binary value relative to the other:

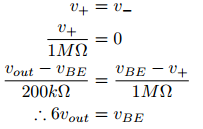

Transconductance Amplifier

As discussed in the theory section, the inverting amplifier's output is given by \eqref{3}. Additionally, the amplifier is in a unity gain configuration, this means that the input resistance to the amplifier is equal to the feedback resistance. Therefore: \begin{equation} V_i=-V_o \end{equation} Furthermore, we want do not want the output to offset the DC base-emitter voltage; therefore, the output resistances make this function as a transconductance amplifier. The circuit realization of this component is the following:

Circuit Diagram

Plots

For some reason I cannot find the plots for this project; however, the hardware did work as intended. The only problems I found were some resoluution issues which could be solved by using a better DAC, one with a 16-Bit resolution could improve this performance.Posted Friday 19 March 2010 by @kilbride_thomas Share

- You might also like: